差動増幅回路をブレッドボードで実験しました。

回路図

ブレッドボード配線図

定電流源に使っているQ3のバイアス回路のR6、R7を12kΩ、33kΩに変更しました。

信号源:

PCM5102A PCM5102Aファンクションジェネレータ+4次バターワースLPF

電源電圧: +4.98V / -4.99V

Q1: 2SC1814 GR (β=417 Vf=691mV) (※)

Q2: 2SC1814 GR (β=417 Vf=693mV) (※)

Q3: 2SC1814 GR (β=380 Vf=689mV) (※)

(※)

AVRトランジスタテスターで測定

入力

ch1:IN1 ch2:IN2

主にch2:IN2に信号波形が現れていて、ch1:IN1はノイズに埋もれてしまっています。

4次バターワースLPFの出力のOUT側をch1、GND側をch2に接続しています。

差動入力なのでこれでいいかと思いましたが、3線のバランス出力(+、-、GND)で出力しないとうまくいかないのでしょうか?

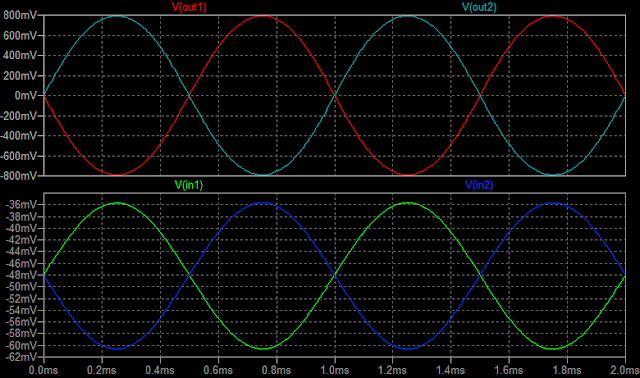

出力

ch1:OUT1 ch2:OUT2

出力はちゃんと差動出力になっています。入力が100mVp-pとすると、OUT1、OUT2それぞれの増幅率Avは Av = 2.18Vp-p / 100mVp-p = 21.8(26.8dB)です。

Trの各端子の電位

Q1、Q2のエミッタ電位

ch1:Ve ch2:OUT2

Q1、Q2のエミッタの電位ch1:Veは-687.6mVで振幅はほとんどありません。AVRトランジスタテスターで測定したVfと近い値になっています。

Q1、Q2のコレクタ電位

ch1:Vc1 ch2:Vc2

Q1のコレクタ電位Vc1の中心値は2.554V、Q2のコレクタ電位Vc2の中心値は3.200Vで656mVの差が出てしまいました。原因はよくわかりません(^q^;

入力を片側だけにする。

信号源からの入力をIN1のみにし、信号源のGND側はGNDに接続しました。

入力

ch1:IN1

出力

ch1:OUT1 ch2:OUT2

出力はOUT1が1.152Vp-p、OUT2が1.144Vp-pで、入力を100mVp-p(信号源の出力は両側に入れた場合からいじっていない)とした場合、OUT1の増幅率Av1、OUT2の増幅率Av2は

Av1 = 1.152Vp-p / 100mVp-p = 11.52(21.2dB)

Av2 = 1.144Vp-p / 100mVp-p = 11.44(22.2dB)

で、差動入力した場合の約半分になっています。←差動入力した場合と片側をGNDに落とした場合は動作が異なる。

オフセット電圧

入力を両方ともGNDに落としてオフセット電圧を測定しました。R2を除去してQ2のベースを直接GNDに落とした場合と比較しました。

R1=10kΩ、R2=10kΩを介してGNDに接地

ch1:Vc1 ch2:Vc2

R2=10kΩのみ除去してGNDに直接接地

ch1:Vc1 ch2:Vc2

R2ありの場合はオフセット電圧は32mVですが、R2を除去した場合は1.501Vと大きなオフセット電圧が発生しました。

OPAMPの反転端子、非反転端子の入力インピーダンスを合わせておけ、というセオリーも納得です(^q^/

OUT1だけを出力として利用

OUT2のコレクタ抵抗R4を除去してOUT1だけ出力として使いました。入力もIN1のみ。

ch1:IN1 ch2:OUT1

シミュレーションと同じく、出力はR4を入れた場合より若干歪んでいる気がしないでもないですが(@@?

周波数特性

信号源をAD9833ファンクションジェネレータ(Bypass出力)に変更して周波数特性を測定してみました。出力が600mVp-p程度なので入力に直列に56kΩのRを入れて減衰させて測定しました。

回路図

@1kHz

ch1:IN1(減衰後) ch2:IN2

増幅率Avは Av = 1.32Vp-p / 64mVp-p = 20.6(26.3dB)。

@1kHzと比較すると測定した最低周波数の500kHzですでに-3dBより下がっているようです。

増幅率が高いのでよくわかりませんが、エミッタ接地回路とくらべても周波数特性は悪化するようです(参考:「

Tr回路の実験 エミッタ接地回路 その2」)

ブレッドボードでの実験の限界も感じます。

測定データ

| F(kHz) |

IN(mVp-p) |

OUT(mVp-p) |

Av |

Av(dB) |

|---|

| 500 |

52 |

268 |

5.153846154 |

14.24262901 |

| 600 |

46.4 |

216 |

4.655172414 |

13.35871541 |

| 700 |

46.4 |

180 |

3.879310345 |

11.77509049 |

| 800 |

48 |

156 |

3.25 |

10.23766722 |

| 900 |

46.4 |

130 |

2.801724138 |

8.948507435 |

| 1000 |

42.4 |

116 |

2.735849057 |

8.741842653 |

| 2000 |

30.4 |

43.2 |

1.421052632 |

3.052203264 |

| 3000 |

21.6 |

27.2 |

1.259259259 |

2.002303058 |

| 4000 |

20.8 |

18.4 |

0.884615385 |

-1.064910239 |

| F(kHz) |

IN(mVamp) |

OUT(mVamp) |

Av |

Av(dB) |

|---|

| 500 |

43.2 |

260 |

6.018518519 |

15.58979202 |

| 600 |

41.6 |

204 |

4.903846154 |

13.81073674 |

| 700 |

38.4 |

168 |

4.375 |

12.81956115 |

| 800 |

37.6 |

144 |

3.829787234 |

11.66349294 |

| 900 |

35.2 |

126 |

3.579545455 |

11.07655763 |

| 1000 |

34.4 |

110 |

3.197674419 |

10.09668485 |

| 2000 |

24 |

40 |

1.666666667 |

4.436974992 |

| 3000 |

14.4 |

24 |

1.666666667 |

4.436974992 |

| 4000 |

13.6 |

15.2 |

1.117647059 |

0.966093591 |

可変電流源

Q3の定電流源を、

自作の可変電流源に置き換えてみましたがうまくいきませんでした。

この差動増幅回路ではうまく使えないのかもしれません。

VEEに引っ張る電流なので、可変電流源の電源の+を差動増幅回路のGND、可変電流源のGNDを差動増幅回路のVEEに接続しました。可変電流源の設定電圧はGNDとVEEを10kΩのPOTで分圧して与えています。

2mA設定時(可変電流源の設定電圧:2.00V)

ch1:OUT1 ch2:OUT2

1mA設定時(可変電流源の設定電圧:1.00V)

ch1:OUT1 ch2:OUT2

1mAに設定したときに出力が歪んでいるのと(2mAの時も歪んでいますが)、OUT2に出力波形が現れていません。

誤算気味(T_T;;;

メモ:

Q3の定電流源の電流を変えてみる(R5の抵抗値を変更)

自作の可変電流源のOPAMPを耐圧の高いものに変更して、電源をVCC / VEEにしてみる。