3枚お願いして3連の状態。基板の穴やVカット、シルクスクリーンなどは当然ながらありません。基板を分割して部品を挿入する穴を開ける必要があります。

基板の分割

以前、アルミ板を切断した方法でやってみました。参考「Nucleo DCO 一旦できたことにする。」

切断するラインに合わせて曲尺をバイスで固定します。

カッターで基板に軽めの力で10回ぐらい切り込みを入れます。

木材の縁を切断するラインに合わせて、パキッと折ります。

アルミのときは片側からの切込みできれいに折れたのですが、ベーク基板の場合はバリが出てしまいました。

材質の差でしょう。余白があるので後で研磨してバリを取ればいいんですが、切れ込みを表裏両方から入れればもっときれいに折れそうな気がします。その際は、表裏の切込みがずれないように注意が必要そうです。

ポンチ打ち

ドリルを入れる前にポンチを打つのですが、いつも使っているポンチはズレやすく径も太いので、アルミ柄の千枚通しを買ってきました。先端が細いのでポンチングする位置を視認するのも楽です。短めのキリとかアイスピックとかでもいいかもしれません。

上からダイソーの精密ハンドドリル(0.8mm)、新調した千枚通し、普通のポンチ。基板の幅は95mmです。

千枚通しは普通のポンチよりやわいので、金属のポンチ打ちには向かないと思いますが、プラスチックならハンマーで打ち込まないで、ねじ込んでポンチングできます。

基板データをプリントアウトして穴の位置を確認しながらポンチを打ちました。

ネジ止め用の基板の端の穴は、ポンチングするときに割れてしまいました。縁は危険です。

ダイソーのハンドドリルで穴あけに挑戦しましたが、穴一つ開けるのも大変です。ダルくなって貫通する前に諦めてしまいました。

ミニルーター

アマゾンで小型のミニルーターが売っていたので試しに買ってみました。出力は低いですが、サイズが小さいのとコードレスなのがメリット。細径のドリルは折れやすいので、1.0mm/Φ2.35のドリルも予備として購入。

電動だと穴あけは瞬殺です(^q^/

↑ポンチ打ちはうまくいったけど3.2mmのドリルを使ってさらに縁が割れてしまった

ただ、千枚通しでポンチングしただけだとドリルの刃先が滑っていらんところを穿孔しがち。最初はいいんですがだんだん削りカスがポンチ穴につまって用をなさなくなってしまいます。

途中からは前述のダイソーのハンドドリルで少しほじってから、電動で穿孔するようにしました。

電動での穿孔は停止時に刃先でポンチ穴を探って、垂直を確保、少し圧をかけてスイッチオン→貫通した感触でドリルを抜く→スイッチオフという風にするのが良さそうです。

今回購入したTacklife PCG01Bは電源スイッチが尻尾の方にあるのと、電源OFFにするのに2秒以上長押ししないといけない点が若干不便です。それでも手動より断然楽ができます。

あと、スイッチを押すと低速から始まりスイッチを押すごとに回転数が上がる仕様なのですが、スイッチ・オン時は一瞬高回転になってから低速になります。これが良いのか悪いのかは使い方次第かな?

↑こういうふうに持たないと片手で電源スイッチを押せない。

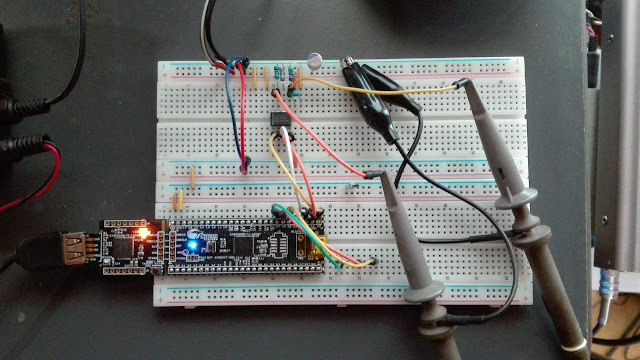

作業時間は、ポンチ打ちが約40分、ドリル穿孔が約60分でした。初回なのでいろいろ失敗してますが、まずまず。この基板も動作確認ぐらいはできそうなのではんだ付けまでやってしまいます。

あと2枚猶予がありますし。

なんだかんだ言って手動のピン・バイスもあったほうがよさそうなので、いずれ購入するつもりです。