https://github.com/ryood/I2S_FG/tree/master/PSoC/I2S_FG/PrototypingKit_DDS.cydsn

PSoCのI2SコンポーネントのDATASHEETではClockの設定の項では

となっていて、192kHz/16bitまでしか選択できない様に書いてあるので仕様外かもしれない。

※WSは2ch分なのでtws=32bitsだと1chは16bitになる。

配線

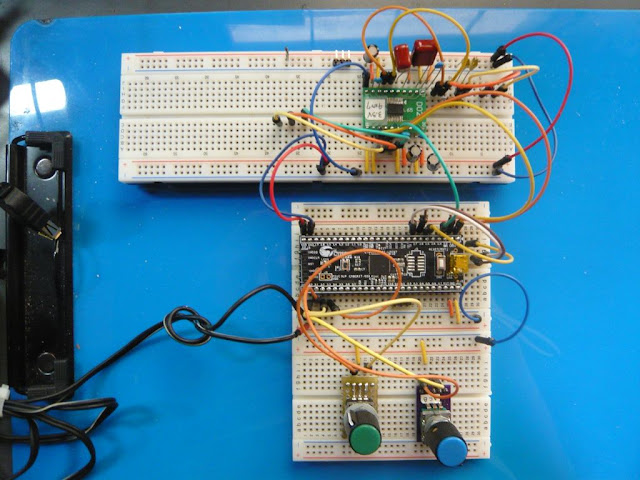

「PSoC 5LP Prototyping KitでPCM5102Aを使ってみる。」のブレッドボード図に周波数設定用のロータリーエンコーダをつないだ。

384kHz/24bit

CPU Clockを72MHz、I2Sコンポーネントに入れるクロックを36MHzに設定。DMAのBUFFER_SIZEを6(byte)に設定。

ch1:SCK ch2:WS

Fsck / Fws = 17.90MHz / 373.1kHz ≒ 48なので24bitを2ch分送信できているようだ。

ch1:SDO ch2:WS

WSがLとHで同じデータが送られているようだ。

ch1:ROUT ch2:LOUT

だいたい10kHzに設定して出力。

384kHz/32bit

CPU Clockを48MHz、I2Sコンポーネントに入れるクロックを48MHzに設定。DMAのBUFFER_SIZEを4(byte)に設定。

ch1:SCK ch2:WS

Fsck / Fws = 23.90MHz / 373.7kHz ≒ 64なので32bitを2ch分送信できているようだ。

ch1:SDO ch2:WS

これもOK

1kHz

ch1:ROUT ch2:LOUT

10kHz

192kHz

I2SのSCKが373.7kHzなので出力周波数がずれているが

1kHz * 373.7kHz / 382kHz ≒ 978.3HzなのでだいたいOKだと思う。

10kHz * 373.7kHz / 382kHz ≒ 9.783kHz

192kHz * 373.7kHz / 382kHz ≒ 187.83kHz

I2Sに入力しているクロック

47.81MHz

メモ:

波形テーブルを作るのがめんどくさかったのでとりあえず16bitのデータに下位bitを0で埋めて出力したので実質16bitのデータ。32bitに拡張しつつ予めバイト順を入れ替えておく。Flashメモリが余っているので波形テーブルの要素数も増やしてみる。

100kHz超えのサイン波を中心に考えて出力にLPFを入れる。←三角波、ノコギリ波は妥協するかLPFをON/OFFできるようにする?

表示用に3.3V駆動のLCDを使いつつノイズにも気をつける。←これもON/OFFできるようにする?

出力レベルの調整はアナログ信号をPOTで減衰させる。←適当な抵抗値を考える。入れる場所をLPFの前段、後段で実験

出力レベルはPSoC内蔵の基準電圧とADCで測定できる?

AVDD-AGNDの電圧を測ると3.10V程度まで低下している。電源には「5V/3.3Vの安定化電源」を使っているのに電圧が低下する原因がわからない。電源からの出力電流は70mA程度。電圧安定度をオシロで見てみる?

0 件のコメント:

コメントを投稿