回路図

基板図

部品面

ハンダ面

抵抗値をあとから変更できるように、結構多めのピンソケットを使いました。

入出力のシミュレーション

負荷抵抗RL=10kΩ、LFOを+2Vp-pののこぎり波とし、Cutoffに加える電圧を-10V、0V、+7.2V、+10Vで、パラメータ解析しました。

シミュレーション回路図

過渡解析

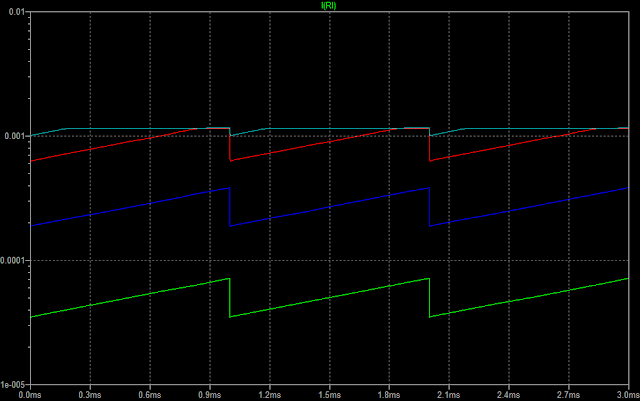

変換カーブが指数関数的になっているかどうか確認するために、縦軸を対数軸としてRLに流れる電流を過渡解析しました。

過渡解析(縦軸は対数軸)

ほぼ、直線になっていると思います。→変換カーブは指数関数的。

測定結果

Cutoff端子に10kΩのPOTをつないで所望の電圧を作り、回路図のOUT端子のGNDに対する電位を測定しました。

電源電圧: -11.59V / +11.73V

負荷抵抗: 10kΩ

Cutoff=9.54V

ch1:IN ch2:OUT

Cutoff=7.20V

ch1:IN ch2:OUT

Cutoff=0V

ch1:IN ch2:OUT

Cutoff=-9.36V

ch1:IN ch2:OUT

シミュレーションと似たような結果になっていると思います。アナログ回路なので誤差はかなりありますが。

DASS01(TLF01)につないで、Anitlog-MMと出音を比較してみる予定です。

0 件のコメント:

コメントを投稿