ステップシーケンサーのKORG SQ-1を購入しました。アナログシンセを使っている人にはコスパが良く、そうでない人にはほとんど使いみちが無い機械です。

今まではDAWのMIDI機能とMIDI-CVコンバーターを使ってシーケンサーとして使っていました。変わった点は、マウス操作ではなくつまみをひねって音を操作出来るようになり、PCも特に必要ではなくなりました。つまみをひねれば音色が変化するアナログシンセとの親和性は非常に高いと言えます。

同梱物は、マニュアル、MIDI-OUT端子変換ケーブル、単3電池×2でした。電源は電池の他USBから供給可能です。

出力信号の観測

CVは5V設定です。設定により、1V、2V、5V、8V(Hz/V)に変更可能です。

GATE信号はH=13V程度出ています。

出力信号 SYNC

SYNC信号はH=5V出力です。パルス幅は13.5msです(仕様では15ms)。正負の極性は設定により変更可能です。

GATE信号の取り扱い

GATE信号は仕様では10Vとなっていますが、無負荷で測定すると13V程度出ています。

自作のEGはGATE信号をArduinoのGPIOに入力する仕様となっているため、H=5Vに制限するようにアダプタを製作しました。

単に10kΩの抵抗をかましただけですが、EG側の入力インピーダンスと合わせてH=5Vとなりました。

またSQ-1のGATE信号の出力インピーダンス(内部抵抗)を計測しようと100Ωの負荷抵抗をつないで出力電圧を計測しましたが、無負荷時と比較してほとんど電圧降下が見られませんでした。出力インピーダンスは無視してかまわないと思います。負荷抵抗100Ωの場合

IO = VO / RL = 13V / 100Ω = 130mA

となり、これ以上流すと危険なので深追いはしていません。おそらく短絡しても保護がかかるようになっているとは思いますが。

SLIDE機能

ステップ間の音程をなめらかにつなぐ機能です。SLIDEをONにしたステップと次のステップが補間されます。

SLIDEをONにしたステップから次のステップにかけてCVがなだらかに補間されています。また、SLIDEをONにしたステップのGATE信号はLに戻らず、次のステップまでHのままになっています。少し凸凹していますが、GATE信号は論理値なので問題ないでしょう。

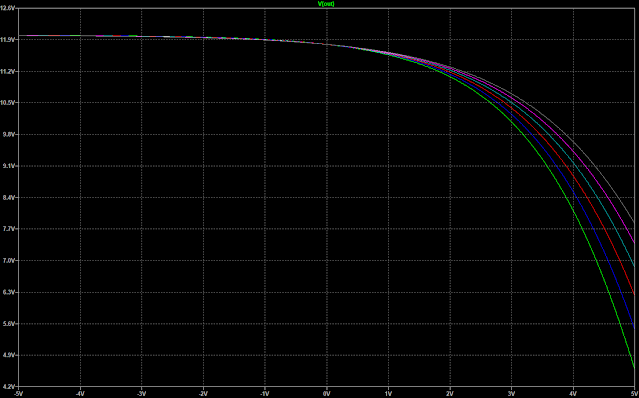

またSEQUENCE MODE (ロータリースイッチ)でCV SLIDEモードを選択するとBチャンネルのプッシュボタンでSLIDE ON/OFF、ノブでカーブのゆるさを変更できます。

Bチャネルのノブ最大→カーブがゆるい

Bチャネルのノブ中間→カーブがシュッとする

音程やフィルターの開閉など、ちょっとしたニュアンスの表現に使えると思います。

メモ

マイコンなどデジタル回路を使ったモジュールを使う場合、GATE信号の13Vに耐えられる仕様にする必要があります。今まで私が作ったものは5V仕様なのでちょっとまずいですね。間違えてCVやAudio用のジャックにGATE信号を入れてしまうことも普通にありそうです。

何らかの保護回路を入れたり、ロジックICなら高耐圧の4000シリーズを使ったりでしょうか。今後の製作物の要件とします。

EGの電源をオフにした場合、入力電圧が低下。AVRは電源OFFの場合GPIOの入力インピーダンスが低くなる?